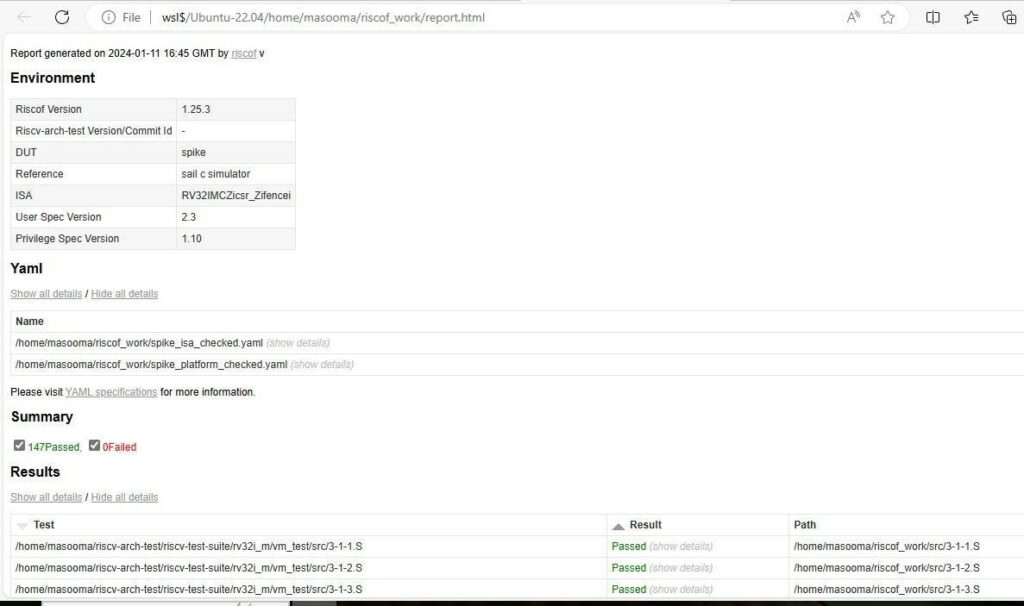

Virtual memory compliance refers to the extent to which the behavior of the virtual memory subsystem specifications is outlined in the RISC-V architecture. Develop customized RISC-V assembly tests that systematically modify permission bits within page table entries. These tests are compiled using the GNU toolchain and executed using the RISC-V assembly code on both the Spike and Sail simulators through the RISCOF framework, facilitating cross-platform analysis. By comparing the resulting log files from the two simulators, we discern any inconsistencies or variations in memory access behaviors. It ensures that the behavior of virtual memory operations, particularly the manipulation of permission bits within page table entries, aligns accurately with the documented expectations and standards of the RISC-V. Their research paper, titled “Virtual Memory Verification – SV32,” delves into the complex mechanisms of virtual memory compliance within the RISC-V architecture.

Virtual-memory-verification-SV32 (MEDS was previously knowned as DDRC)